# **ATX7006**

ATX-Express ATX-Hybrid

# **User manual**

Revision 2.16 March 2016

APPLICOS bv, Veldkampseweg 1, 8181LN, Heerde, The Netherlands

# 1 Table of Contents

| 1 | Table o        | of Contents                                         | 2  |

|---|----------------|-----------------------------------------------------|----|

| 2 | Genera         | al information                                      | 5  |

|   | 2.1            | Update information                                  | 5  |

|   | 2.2            | Theory of operation                                 | 5  |

|   | 2.3            | Test methods                                        | 6  |

|   | 2.3            |                                                     |    |

|   | 2.3            |                                                     |    |

| 3 | 2.3<br>Case at | 3.3 Measurement timing  Ind controller description  |    |

| • | 3.1            | ATX7006                                             |    |

|   | 3.1            |                                                     |    |

|   | 3.2            | ATX-Express                                         | 10 |

|   | 3.2            | 2.1 ATX-Express Controller                          | 10 |

|   | 3.3            | ATX-Hybrid                                          |    |

|   | 3.3<br>3.3     |                                                     |    |

|   | 3.3            |                                                     |    |

|   |                | Controller settings                                 |    |

|   | 3.4            | 4.1 Setup of USB communication                      | 13 |

|   | 3.4            | 0 1                                                 | 15 |

|   | 3.4            |                                                     |    |

|   | 3.5            | ATX Power supply                                    |    |

|   | 3.5<br>3.5     | J                                                   |    |

|   | 3.5            |                                                     |    |

| 4 | Module         | e descriptions                                      |    |

|   | 4.1            | Digital I/O module                                  |    |

|   | 4.1            |                                                     |    |

|   | 4.1<br>4.1     |                                                     |    |

|   | 4.1            |                                                     |    |

|   | 4.2            | DIO II module                                       |    |

|   | 4.3            | AWG20 20-bit/2Msps Arbitrary Waveform Generator     | 27 |

|   | 4.4            | AWG22 22-bit/2Msps Arbitrary Waveform Generator     | 30 |

|   | 4.5            | AWG18 18 bit / 300Msps Arbitrary Waveform Generator | 31 |

|   | 4.6            | AWG16 16 bit / 200Msps Arbitrary Waveform Generator | 35 |

|   | 4.7            | WFD20 20bit / 2Msps Waveform Digitizer              | 37 |

|   | 4.8            | WFD22 22bit / 1Msps Waveform Digitizer              | 39 |

|   | 4.9            | WFD16 16-bit / 180Msps Waveform Digitizer           | 41 |

|   | 4.10           | ,                                                   |    |

| _ | 4.11           | Dual Power Supply module (DPS)                      |    |

| 5 |                | rement set-up                                       |    |

|   | 5.1<br>5.1     | Setup the stimulus generator                        |    |

|   | 5.1<br>5.1     |                                                     |    |

|   | 5.1            | 1.3 Setup the stimulus address counters             | 58 |

|   | 5.1            | · · · · · · · · · · · · · · · · · · ·               |    |

|   | 5.1<br>5.1     |                                                     |    |

|   | ე. I           | 1.0 Setup of capture loop and fatericy counters     |    |

| 5.1.                 | ./ Setup of the stimulus generator the commands to use, step by step                                                                                                                                      | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                                                                                                                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.                 | 2 Initialize and connect reference and power supply channels                                                                                                                                              | 74<br>74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.4.<br>5.4.<br>5.4. | Calculation-parameter and -options definition                                                                                                                                                             | 78<br>78<br>87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1                  | Overview                                                                                                                                                                                                  | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                                                                                                                                                                                                           | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.1                  | DIO module, inputs, outputs                                                                                                                                                                               | 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.2                  | Specifications AWG22 module                                                                                                                                                                               | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.3                  | Specifications AWG20 module                                                                                                                                                                               | 181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.4                  | Specifications AWG18 module                                                                                                                                                                               | 181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.5                  | Specifications AWG16 module                                                                                                                                                                               | 181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.6                  | Specifications WFD22 module                                                                                                                                                                               | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.7                  | Specifications WFD20 module                                                                                                                                                                               | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.8                  | Specifications WFD16 module                                                                                                                                                                               | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.9                  | Specifications Dual reference source module                                                                                                                                                               | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.10                 | Specifications Dual power Supply module                                                                                                                                                                   | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      | 5.2<br>5.2<br>5.3<br>5.3<br>5.3<br>5.4<br>5.4<br>5.4<br>5.4<br>5.4<br>5.4<br><b>Comma</b><br>6.1<br>6.2<br><b>Comma</b><br><b>Specific</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9 | 5.2 Digital IO Pattern Generator and Data IO setup. 5.2.1 Setup the measurement timing with the Pattern Bit definition 5.2.2 Setup static output lines (SDO).  5.3 Initialize and connect signal module channels. 5.3.1 Initialize and connect analog frontend of stimulus or capturing channels. 5.3.2 Initialize and connect reference and power supply channels. 5.3.3 Start the measurement.  5.4 Post measurement steps. 5.4.1 Set modules back in configuration mode. 5.4.2 Calculation-parameter and -options definition. 5.4.3 Start calculation. 5.4.4 Read out measurement and calculation results.  Command reference. 6.1 Overview. 6.2 General Syntax.  Command descriptions.  Specifications.  8.1 DIO module, inputs, outputs. 8.2 Specifications AWG22 module. 8.3 Specifications AWG20 module. 8.4 Specifications AWG18 module. 8.5 Specifications AWG16 module. 8.6 Specifications WFD22 module. 8.7 Specifications WFD20 module. 8.8 Specifications WFD16 module. 8.9 Specifications Dual reference source module. |

# LIABILITY DISCLAIMER

The product described in this manual is warranted in accordance with the terms as set forward in applicable quotations or purchase orders. Product performance is affected by configuration, application, software control, and other factors. The suitability of this product for a specific application must be determined by the customer and is not warranted by APPLICOS.

APPLICOS shall not be liable for any special, incidental or consequential damage.

Information in this manual is intended to be accurate and reliable. However APPLICOS assumes no responsibility for any errors, which may appear in this document nor does it make any commitment to update the information contained herein.

# 2 General information

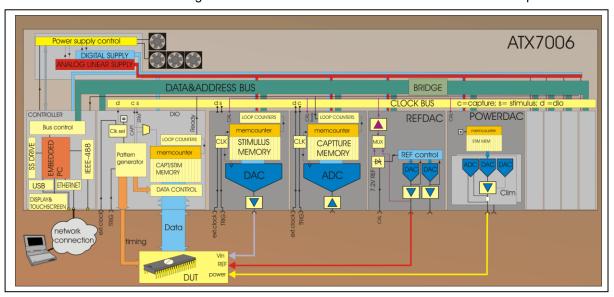

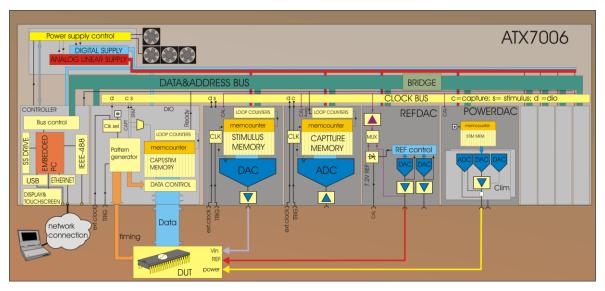

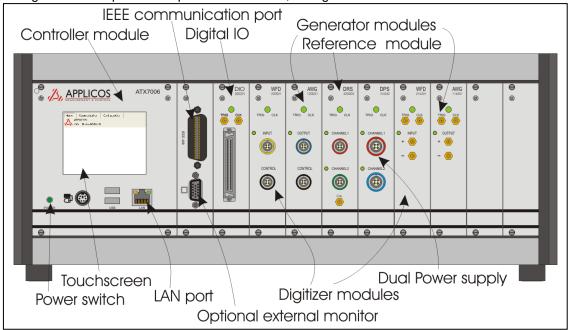

The ATX7006 is fully integrated system containing all hardware for testing A/D and D/A converters. The controller module runs the Windows XP operating system and controls the complete system including communication, signal calculation, and measurement result analysis.

Via Ethernet or GPIB, the ATX communicates with a pc or tester. Software on the PC gives an easy to use graphic interface and measurement setup tools.

Equipped with the standard ATX7006 modules, the system is suitable for testing A/D and D/A converters of 16 bit or more. The test speed is programmable up to 2MHz. Various analog modules are available to cover measurements from DC up to 400Msps

# 2.1 Update information

ATX7006 features and commands are added, adjusted and extended on a regularly basis. On <a href="https://www.atx7006.com">www.atx7006.com</a>, the latest manual version and a complete ATX command overview can be found. The site also contains articles, frequently asked questions and application notes. It is recommended to check the site regularly, to be informed about the latest developments.

# 2.2 Theory of operation

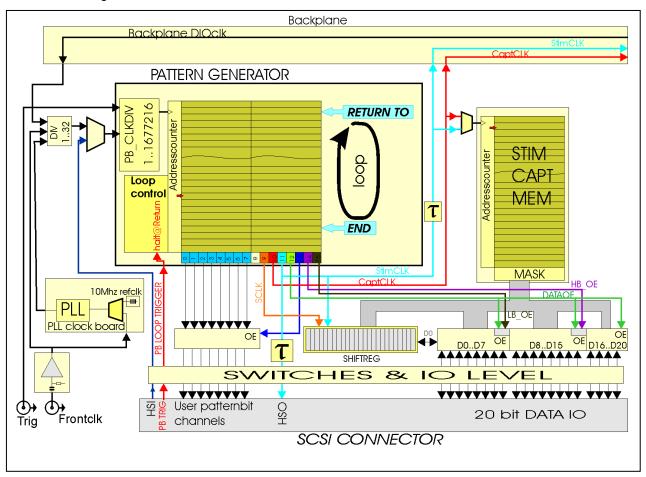

The ATX7006 is controlled by a PC or by means of commands sent via Ethernet or IEEE-488 communication. The block diagram shows the basic structure of an ATX7006 test setup.

The controller receives commands for setting up the measurement, calculates the desired stimulus waveforms and stores it to the appropriate sourcing module, and sets up the modules for the measurement. Storage of more than one stimulus signal in one module is possible.

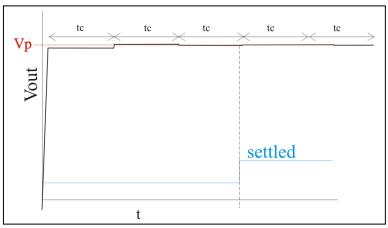

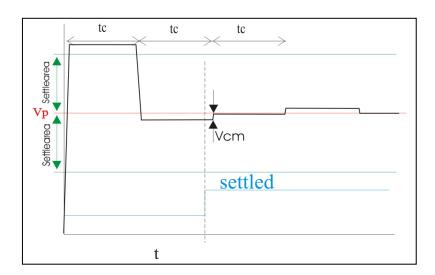

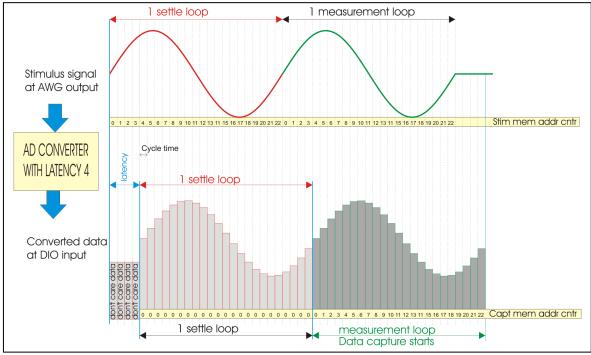

In each generating or capturing module, loop counters are built in for applying or capturing a signal repeatedly during settling (settle loops) or measurement (measurement loops)

When all settling and measurement loops are captured, a "ready" signal is set active by the capturing module, indicating the end of the measurement.

The digital IO module has a double function. The module captures digital results or sources digital stimulus the Device Under Test (DUT). An addition to this, the DIO has control over the timing of the measurement by means of a built-in, user-programmable Pattern Bit Generator.

The Pattern Generator generates 8 universal signals that are available for synchronization between the ATX7006 and the DUT (i.e. start conversion). 7 dedicated Pattern Bit channels are used for

internal synchronization and IO data control, 2 of which are the capture and stimulus-clock, both lead through the backplane to clock the generator and digitizer modules. Other dedicated clocks are used for serializing or de-serializing in the data path between DUT and capture/stimulus memory.

The clock source for the Pattern Generator can either be the internal 200MHz clock, a user applied front clock or a backplane clock. This backplane clock can be driven by one of the modules in the system.

After the measurement, the results are read from the capturing modules and analysed by the controller by means of several implemented calculation algorithms.

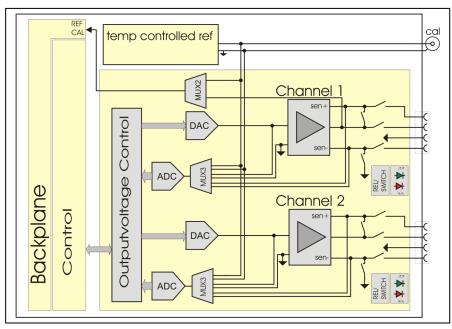

Besides capturing and generating modules, an ATX carries a reference module with a high precision temperature controlled reference source, from which two programmable reference channels are derived. The reference module is also used as the reference source for auto calibration of the ATX modules.

A Power supply module with two independent channels is available for powering the device under test. The module has options for PSRR measurements, current measurements and current limited operation. The maximum channel output current is 200mA.

The system is powered by a unique power supply, consisting of a low noise linear analog power supply block for the analog module frontends and a powerful switching supply that provides power to the digital part of the ATX modules. System Power supply current can be monitored. Also the fans in the ATX system are controlled from the power supply module.

## 2.3 Test methods

The tests available in the ATX are various. The test method, dynamic or linear, is determined by the type of stimulus signal that is applied to the DUT and the calculation algorithm chosen for the analysis of the captured results. The timing of the measurement in normal DIO mode operation is determined by the programming of the Pattern Generator.

# 2.3.1 Analog to digital tests

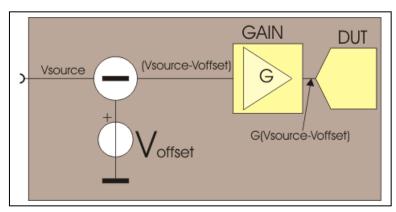

For A/D tests, the DIO is the capturing module and should be set to input. Prior to the measurement a waveform generator module is loaded with one or more stimulus signal(s). During the measurement, the content of the stimulus memory is converted, the analog signal and appears at the module output. Optionally an additional offset is added to the stimulus signal. The converter data can either be captured parallel, byte wise or serial. After the measurement the contents of the DIO memory is analyzed. If the device under test generates two's complement code, the DIO data control box can perform an XOR function over the captured data, inverting the MSB.

# Available signal types:

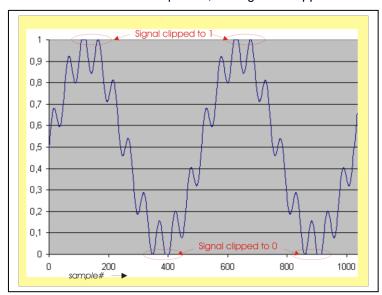

# **Analog ramp**

Defined with number of steps, start and end voltage or by start voltage and voltage increment. This type of signal is commonly used for D/A linearity tests and statistical tests.

For *linearity tests*, the ramp steps should be of a higher resolution than the converter under test. The resolution of the ramp steps is dependent on the chosen AWG output range, and the number of steps used.

For *statistical tests*, multiple ramps can be stored the stimulus memory. Alternatively the stimulus contents can be applied repeatedly. The DIO memory then stores a multiple of the applied ramps. The statistical parameter consists of the number of occurrences of each code in the measurement array.

#### Analog sine wave

Defined by number of stimulus steps, number of periods within this stimulus, offset, amplitude and phase. for FFT purposes, the number of steps preferably is a power of 2 number. The number of periods used is preferably a prime number. This signal type is commonly used for A/D dynamic tests

#### Analog triangle wave

Defined by number of stimulus steps, number of periods within this stimulus, offset, amplitude, phase and symmetry.

### **Analog Square wave**

Defined by number of stimulus steps, number of periods within this stimulus, offset, amplitude, phase and symmetry.

# Available linearity calculation methods:

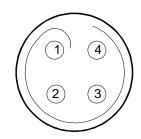

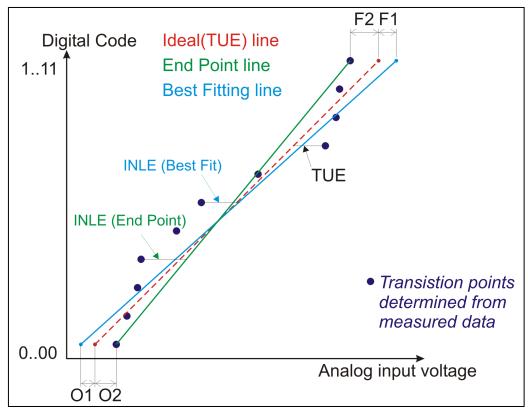

#### A/D linearity calculation

The calculation delivers parameters like gain-, offset- and full-scale error, INLE, DNLE, TUE. Additionally, a report of missing codes can be generated. Error calculation can be performed using an endpoint line or a best fitting line. Additionally, an array containing the deviations from the chosen reference line is available

With several ramps in one measurement it is possible to perform statistical parameter calculations.

#### A/D dynamic calculation

This calculation delivers parameters like SINAD,THS,SND,SFDR Peak distortion Peak Spurious and ENOB. Additionally, the complete FFT array and list of harmonics are available.

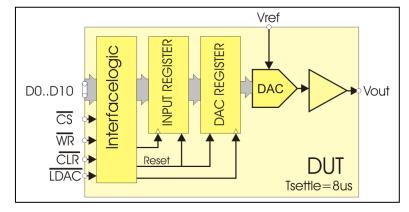

# 2.3.2 Digital to Analog Tests

For D/A tests the DIO is the sourcing module and should be set to output. Prior to the measurement a DIO stimulus memory is loaded with one or more signals. During the measurement, the content of the memory is put via the ATX digital output to the DUT. The data can be applied either parallel, byte wise or serial.

If the device under test needs two's complement code, the DIO data control block can perform an XOR function over the stimulus, inverting the MSB. Additionally unused bits can be masked out with an AND function.

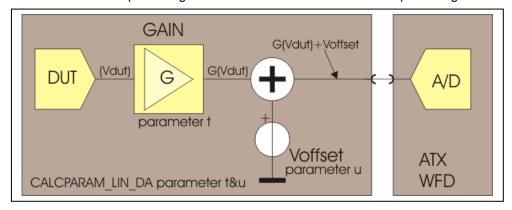

After the measurement the contents of a digitizer module memory is analyzed.

#### Available signal types:

#### Digital ramp

Defined with number of steps, start and end code or by start code and code increment. A digital ramp commonly used for D/A linearity tests. For averaging purposes, it is possible to define a ramp that applies the same code multiple times. The ramp increment value should then be fraction. Alternatively the stimulus contents can be applied repeatedly.

#### Digital sine wave

Defined by number of stimulus steps, number of periods within this stimulus, offset code, amplitude and phase. The digital sine wave signal is used for D/A dynamic tests. For FFT purposes, the number of steps is preferably a power of 2 number. The number of periods used is preferably a prime number.

#### Digital triangle wave

Defined by number of stimulus steps, number of periods within this stimulus, offset, amplitude, phase and symmetry.

#### **Digital Square wave**

Defined by number of stimulus steps, number of periods within this stimulus, offset, amplitude, phase and symmetry.

#### Available calculation methods:

Calculation procedures are implemented for measurement result analysis. After calculation, the calculated error plots and error parameters are available.

#### D/A linearity calculation

This calculation delivers the gain- and offset error, full scale error, INLE, DNLE, TUE.. With several ramps in one measurement it is possible to perform statistical parameter calculations.

### D/A dynamic calculation

This calculation is not different from the A/D dynamic calculation. In fact, the same calculation commands are used, resulting in the same parameters SINAD,THS,SND,SFDR, Peak distortion, Peak Spurious and ENOB.

Chapter 4 will describe in detail how to setup the calculation and retrieve the calculation results.

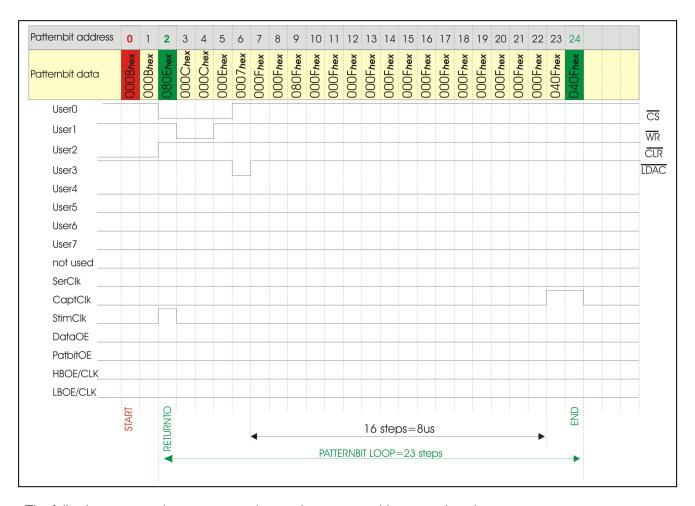

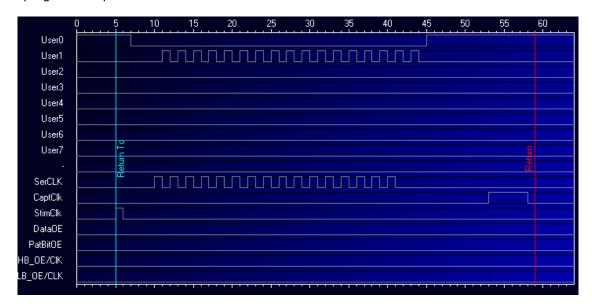

# 2.3.3 Measurement timing

During the test, a user-defined stimulus signal (digital or analog) is applied to a converter under test.

The dedicated ATX7006 StimClk Pattern Bit is used for clocking the stimulus signal in the generating module.

The DUT converts each applied sample, optionally controlled by one or more of the eight user available Pattern Bit channels.

The converted result is captured and stored in the memory of the capturing module. The timing of capture and storage is controlled with CaptClk, one of the dedicated Pattern Bit channels.

Both CaptClk and StimClk are controlled by the Pattern Generator and available on the backplane of the ATX7006.

More dedicated Pattern Bit channels may be needed, i.e. to (byte wise) latch the incoming data or to clock the serial data. The use and function of the Pattern Bit channels are discussed in more detail in the section "Setup the measurement timing with the Pattern Bit definition"

# 3 Case and controller description

There are three ATX models:

- ATX7006 a nine slots fully integrated test solution with GPIB and Touchscreen.

- ATX-Express a five slots fully integrated test solution.

- ATX-Hybrid a seven slots ATX combined with 6 user assignable PXI slots.

This chapter explains the differences and similarities between the three models.

## 3.1 ATX7006

The ATX7006 case has space for a maximum of 9 modules. The controller is provided with a touchscreen to see the ATX status and change settings from the ATX 7006 Controller.

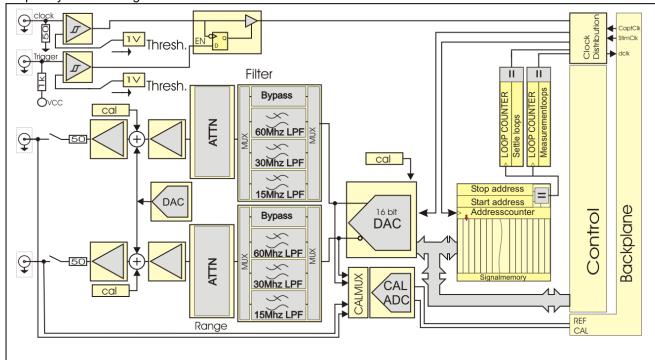

Figure 1 ATX7006 block diagram

### 3.1.1 ATX7006 Controller

The controller module is a Windows-XP™ based controller unit that has control over the ATX7006 specific backplane bus.

After switching on the ATX7006 with the power switch on the backside, the Power supply starts up the standby voltage. In standby mode, the Controller power switch LED lights up yellow. The ATX can then be switched on by pressing the power switch. The power switch led then lights green. When the power switch is pressed again the ATX shuts down and the power supply then switches over to standby mode. Avoid switching off the system with the backside main switch when the ATX is not in standby mode.

After power up, the controller starts the operating system and then starts the ATX7006 firmware application. This application controls the modules in the system, handles all communication, calculates stimulus signals and performs signal analysis calculations

Communication is established via GPIB (IEEE communication port) or Ethernet. To establish communication using the Ethernet connector, the ATX can be connected to a local network. For a direct communication link between a PC and the ATX, a crosslink Ethernet cable or optionally an USB to Ethernet adapter can be used.

# 3.2 ATX-Express

The ATX-Express is a smaller version of the ATX7006. The ATX-Express case has space for a maximum of 5 modules. To see the ATX status and change settings from the ATX-Express Controller a mouse, keyboard and monitor must be connected.

# 3.2.1 ATX-Express Controller

The controller module is a Windows-XP™ based controller unit that has control over the ATX-Express specific backplane bus.

After switching on the ATX-Express with the power switch on the backside, the Power supply starts up the standby voltage. In standby mode, the Controller power switch LED lights up yellow. The ATX can then be switched on by pressing the power switch. The power switch led then lights green. When the power switch is pressed again the ATX shuts down and the power supply then switches over to standby mode. Avoid switching off the system with the backside main switch when the ATX is not in standby mode.

After power up, the controller starts the operating system and then starts the ATX-Express firmware application. This application controls the modules in the system, handles all communication, calculates stimulus signals and performs signal analysis calculations

Communication is established via Ethernet. To establish communication using the Ethernet connector, the ATX can be connected to a local network. For a direct communication link between a PC and the ATX, a crosslink Ethernet cable or optionally an USB to Ethernet adapter can be used.

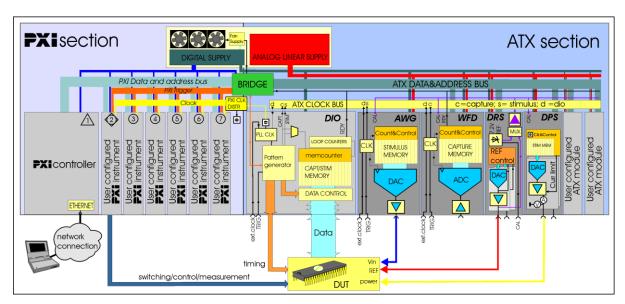

# 3.3 ATX-Hybrid

The ATX-Hybrid is a combination from the ATX7006 and a PXI rack. The ATX-Hybrid has a 7 slot ATX- section for high performance ATX-modules and a 6 slot PXI section that allows usage of the many general-purpose PXI-modules available in the market.

A special bridge on the backplane makes the connection between the PXI side and the ATX side. By bridging clocks and triggers between the two sections, a full integration between ATX- and PXI resources is achieved.

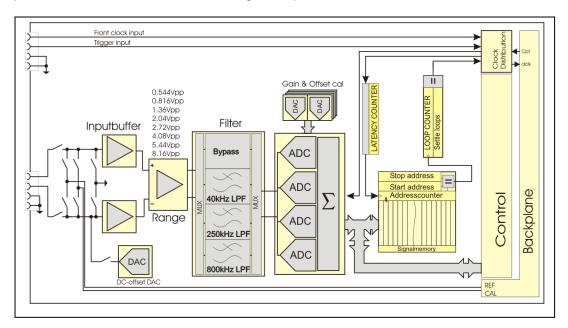

Figure 2 ATX-Hybrid block diagram

# 3.3.1 ATX-Hybrid controller

The controller for the ATX-Hybrid is a standard PXI System Controller. On this controller the ATX-Hybrid firmware application is installed. This application controls the modules in the system, handles all communication, calculates stimulus signals and performs signal analysis calculations

Communication is established via Ethernet. To establish communication using the Ethernet connector, the ATX can be connected to a local network. For a direct communication link between a PC and the ATX, a crosslink Ethernet cable or optionally an USB to Ethernet adapter can be used.

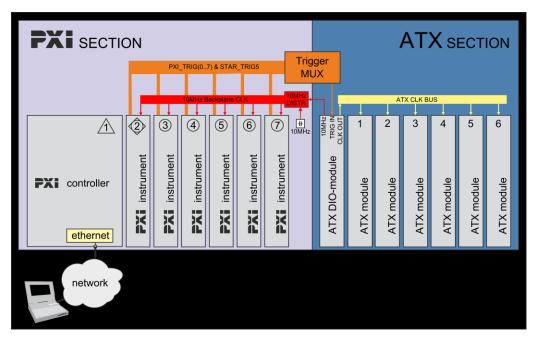

# 3.3.2 ATX-Hybrid clock synchronization

By synchronizing the 10MHz reference clock between the ATX- and PXI section, a coherent measurement with ATX and PXI modules is achieved. The main clock generator for the ATX section is the ATX DIO-module. The ATX DIO-module has a on board 10MHz high precision temperature controlled oscillator. When the ATX DIO-module is in the ATX Hybrid, this module delivers the 10MHz reference clock to the PXI section through the backplane. All the PXI-modules that use the 10MHz backplane clock as reference are now synchronized to the ATX DIO-module. If there is no ATX DIO-module in the Hybrid system a 10MHz clock on the backplane takes over. (see Figure 3)

# 3.3.3 ATX-Hybrid trigger interconnection

Setting up a measurement with PXI instruments and ATX modules can be done by using the PXI triggers. Different PXI triggers can be used to trigger the ATX section. With the commando **PXI\_TRIG** the PXI trigger source can be selected. With the **CTRIG** command the PXI trigger can be selected as trigger source for the DIO. It is not possible to trigger a PXI instrument by the DIO because there is no trigger output on the DIO module. (See Figure 3)

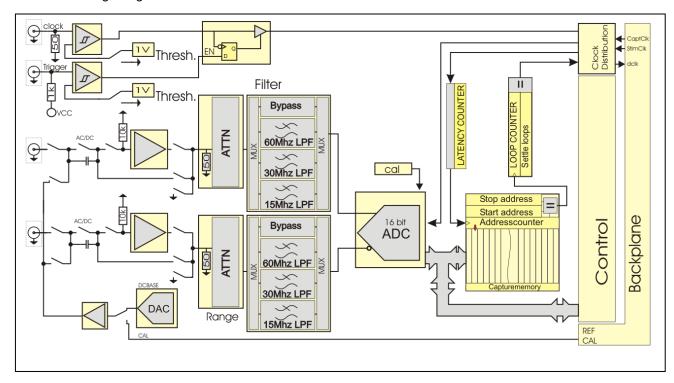

Figure 3 Hybrid Trigger and clocking

# 3.4 Controller settings

Every ATX model has the same software running on the controller. Depending on the model the system has an internal screen or an external monitor but the settings are the same..

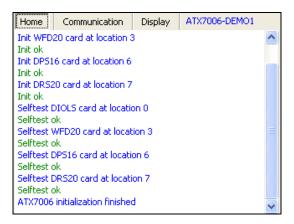

Depending on the display settings, the touchscreen display shows the **"Home"** window giving status information of the ATX, command interpretation and the installed modules.

The tabs on top of the window, lead to communication and display configuration settings. Selections can be made using the touch screen, or a mouse.

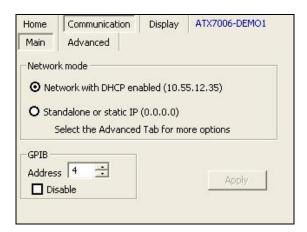

To change the communication settings, select the *communication tab* and the communication settings window opens. The GPIB communication can be enabled and the used GPIB address can be configured. Alternatively, the commands **GPIB\_ADDR** and **GPIB\_STATUS** can be used for this. The network configuration settings can be found in this tab.

Most network connections will be provided with a DHCP server. Select "Network with DHCP enabled". This is the default setting.

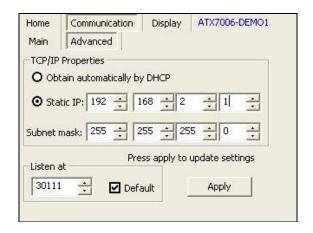

If a static IP is required, or if a USB communication is preferred, the Standalone mode should be selected. In that case, the IP address and subnet mask should be filled in at the "Advanced" tab.

An example of a valid subnet is 255.255.255.0. This value should correspond with the subnet mask on the client (pc) side. A valid IP address could be 192.168.2.2.

The corresponding commands for the network configuration are LAN\_STATICIP, LAN\_DHCP and LAN\_SUBNETMASK.

It is also possible to change the default port at which the ATX7006 is listening for incoming data, on the "Advanced" tab. The corresponding command to change the port is **LAN\_PORT**.

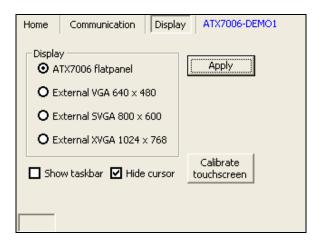

The "Display" tab allows to configure the display setup of the ATX7006.

When an external display is connected and selected to be used, the ATX7006 flat panel is disabled. The touch screen calibration can also be started in this window. This calibration is to link the sensed touch screen sensor coordinates to the right spot on the screen. The software of the touchscreen interface "learns" which spots on the touch sensor overlay which spots on the screen.

# 3.4.1 Setup of USB communication

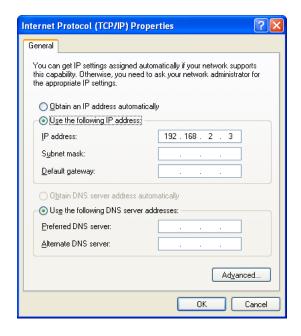

For USB communication with the ATX7006 system, a Network USB adapter is provided. Please connect the USB cable to your PC and connect the network side with a cross link cable to the ATX7006. The ATX7006 should be configured in Standalone/Static IP network mode (see description **above**). On the pc side follow the next steps:

- Go to Control Panel -> Network Connections and select the Local Area Connection of the Sitecom USB to Ethernet adapter

- Double click this icon select properties. Then select Internet Protocol (TCP/IP).

- Click on Properties and select "Use the following IP address:"

- Fill in e.g. **192.168.2.3** for the IP address and **255.255.255.0** for the Subnet mask. The subnet mask should correspond with the subnet mask on the ATX7006, while the IP address should be different from the ATX7006 IP address.

- Click on the Advanced button and select the tab WINS

- At the NetBIOS settings, select the second item "Enable NetBIOS over TCP/IP"

- Click Ok, again Ok and Close If the ATX7006 is configured with a static IP (e.g. 192.168.2.2)

Now, communication should be possible by using the IP address or NetBIOS name.

# 3.4.2 Setting up ATX communication in ATView7006/ATCom7006

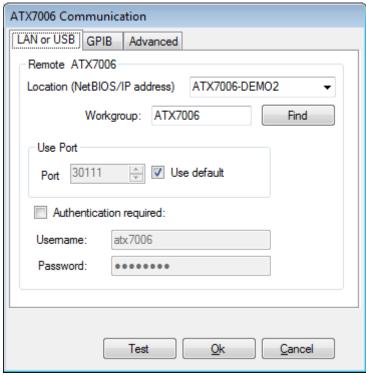

Start ATView7006 and from the menu, select [Options]→[Communication settings]. Alternatively, these settings can be configured in ATCom, using [File]→[Communication]. The configuration dialog opens:

Type the ATX NetBIOS name or IP address in the location field. The NetBIOS name can be found in the upper-right corner of the ATX7006 controller display. On the ATX-Express the NetBIOS name can be found on the controller handle label.

Alternatively, the dialog can find all ATX systems in a specified workgroup. For this, specify the workgroup name in the workgroup field and click find. (This will take some time). After this, the ATX system can be selected from a list in the location field.

Optionally, the ATX server port can be specified. This port is set to 30111 by default. Authentication is disabled by default on the ATX. Authentication can be configured using the commands LAN USER and LAN ENABLEAUTH.

Press "Test" to check if communication settings are correct.

For GPIB communication settings, select the GPIB tab. In this tab, GPIB address and communication timeout can be configured. Note that the entered GPIB address should correspond with the GPIB address setting in the ATX. The GPIB address factory setting is address 4. To change this address, use the command GPIB\_ADDR. Alternatively, these settings can be changed using the ATX7006 touch screen, as described in section **3.4**.

### 3.4.3 How to copy files to the ATX7006

For using the ATX commands **EXECUTE\_CMDFILE** and **EXECUTE\_SCRIPT**, the user needs to copy the desired command file(s) or lua script file to the ATX system. For this, a connection should be established for file transport. There are two possible ways to establish such a connection with the ATX7006:

- Network sharing

- FTP connection

#### **Network sharing**

By default, the ATX7006 has network sharing for the **userdata** folder enabled. Please browse to the workgroup ATX7006 (default) and select the ATX7006. A username and password is required to get

access. The Network sharing username and password is a windows setting. The password and username for network sharing is *atx7006*.

#### **FTP** connection

The ATX7006 has a build in ftp server. To start this server, refer to the command FTP (FTP START to start the server listening on the default port 21). Again, the default start folder of the ftp server is "userdata". If the ATX7006 LAN communication is not protected with a specified username and password, use the default username and password. The default Username is **atx7006**, the default password is **atx7006** as well. If the ATX7006 LAN communication is protected with a password, please use the corresponding username and password.

LAN usernames and passwords are managed with the command LAN\_USER.

#### file location.

As described above, the user file **source** directory is located on the ATX7006 system: **c:/userdata.** When using a command or Lua file, a complete filename should be entered, including the file extension and the path *under* the user data directory (excluding the folder name c:/userdata).

#### Example:

To run a command file named **test.cmd**, located in ATX folder **c:\userdata\cmdfiles**: **EXECUTE CMDFILE cmdfiles\test.cmd**

# 3.5 ATX Power supply

The power supply of the ATX systems consists of a switching and a linear section. The switching supply provides the controller module and digital section of the modules. The linear section provides the Analog section of the modules.

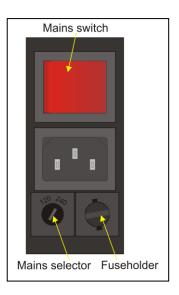

# 3.5.1 On/off switching ATX7006 / ATX-Express

The main power switch is situated on the ATX Back panel. When switched on, the digital supply starts up the standby supply voltage. The controller power switch-led lights up yellow. The primary part of the analog supply also switches on, but the regulator circuitry is disabled. When the power switch on the controller module is pressed, the ATX supply switches over from standby to on. All digital and analog supplies are switched on and the fans start to run. The controller power switch-led then lights up green. The ATX starts up the operating system and the application software. **Switching off the ATX with the backside main power switch while the ATX is not in standby mode should be prevented.** To shut down, first press the front power button. The operating system is shut down and then the power supply switches back to "stand-by". After this, the power supply main switch can be switched off.

The supply current can optionally be monitored by means of the command PS CURRENT.

# 3.5.2 On/off switching ATX-Hybrid

The main power switch is situated on the backside from the ATX Hybrid. When switched on all digital and analog supplies are switched on and the fans start to run. The ATX-Hybrid starts up the operating system and the application software. **Switching off the ATX-Hybrid with the backside main power switch while the ATX is not properly shut down should be prevented.** To power off, first shut down the operating system. When the operating system is shut down then the power supply main switch can be switched off.

# 3.5.3 ATX mains voltage select

#### Mains selector (110-240V Mains voltage)

The factory setting of the mains selector is the 240V, unless agreed otherwise. For a mains voltage of 110-120V, the mains selector should be switched to "120" using an average-size blade screwdriver. The fuse rating should correspond to the mains voltage selected.

Caution: Always operate the ATX7006 with the correct mains voltage. A mains voltage higher than selected with the mains selector may result in damage to the ATX.

## Fuse replacement (110-240V Mains voltage)

The fuse should always be replaced with the same type and value. The replacement fuse should be of a Antisurge (T) 20mm x 5mm Ceramic type. The current rating is dependent of the mains voltage selected:

220-240V: 2.5A 110-120V: 5A

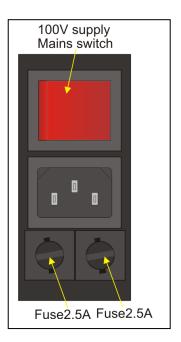

# 100V Mains supply

In case of a 100V mains supply, the mains voltage should be at least 96V. The maximum allowed mains voltage is 110V. **Operation with incorrect mains voltage will result in damage to the ATX7006.**

At the Power entry, a second fuse holder is situated at the mains selector position.

The fuses should always be replaced with the same type and value. The replacement fuse should be of a Antisurge (T) 20mm x 5mm Ceramic type . For a 100V mains voltage, the current rating is :

Left fuse: 2.5A (Analog supply)\* Right fuse: 2.5A (Digital supply)

\*The fuse should have a minimum I<sup>2</sup>t value of 14. Recommended Fusetype is Littlefuse 213 series with "Time lag surge withstand".

# 4 Module descriptions

The ATX7006 is a modular system. In this section, the modules are described in detail. The figure below represents a possible ATX7006, configuration.

The ATX has space for modules of various kind. The first available slot position is assigned to the DIO module. The remaining slots are universal and can be assigned unrestrictedly.

# 4.1 Digital I/O module

The DIO module can operate in the following configurations:

# Low speed mode (DIOLS)

In this mode, both capture and stimulus mode are supported. The data IO lines can be programmed as input or output and can support up to 20-bit parallel or 24-bit serial formats. By default, the capture and source memory depth is b 4M-words x 24bit. Using the **DIO\_IOMODE** command, it is possible to select a memory depth of 8M-words x16 bit. This option is supported from DIO FPGA revision 8 (see **CID**) and higher and firmware release 1.26 and higher.

The maximum data rate is 50MHz while the maximum Pattern Generator input clock frequency is 100MHz. The single ended IO levels are programmable to support 3.3V to 5V CMOS.

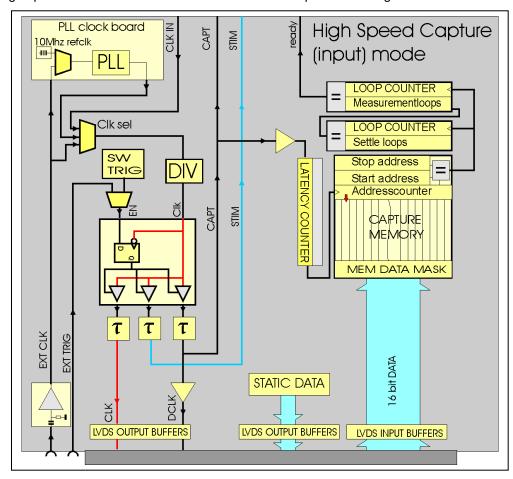

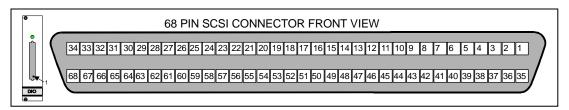

# High speed (DIOHS) Capture mode

In the High speed capture mode, the DIO memory captures measurement data. The data width is maximum 16-bits and is captured parallel on the SCSI connector. All inputs are operating in LVDS format.

The measurement timing is controlled using delay lines. The maximum data rate is 200MHz.

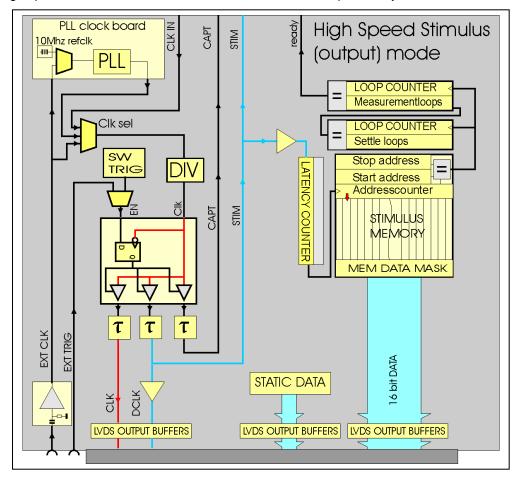

### High speed (DIOHS) Stimulus mode

In the High speed stimulus mode, the DIO memory holds stimulus data. The data width is maximum 16 bit and is applied parallel on the SCSI connector. All outputs are operating in LVDS format. The measurement timing is controlled using delay lines. The maximum data rate is 200MHz.

By default, the DIO module starts in the DIOLS mode. When the operational mode is changed, the module FPGA is reloaded automatically. Refer to the DIO\_OPMODE command for more information.

#### **DIO Front panel led**

The DIO has one LED on the front panel, indicating the DIO status.

off Module is in configuration mode.

green Module is in measurement mode.

red During power-up and at FPGA (re)load.

### 4.1.1 DIO Clock source board

Every DIO has an on board 200MHz crystal oscillator that generates a basic clock for the module. Beside this oscillator, there is a clock source board.

On older DIO models this clock source board holds crystal oscillators of 120MHz, 140MHz , 160MHz and 180MHz.

Newer DIO modules are equipped with a PLL clock generator board, which can generate virtually any clock frequency between 2kHz to 945MHz. This PLL also emulates the legacy oscillator clock sources, if they are selected.

The older modules can be recognized by their FPGA revision: in low speed mode, they have an FPGA revision below 5, in high speed mode the FPGA revision is below 4.

The clock source can be selected with CCS. The PLL frequency can be set with DIO\_PLL\_FREQ.

# 4.1.2 Digital I/O module in low speed mode

In low speed mode, the DIO module operates in a Pattern Generator based configuration. The figure illustrates a simplified block diagram of the DIO in this configuration.

#### **Pattern Generator**

The measurement timing is controlled by the programming of the Pattern Generator . The timing of one sample consists of one pattern memory loop through a user defined part of the pattern memory. The Pattern Bit memory depth is 256kWord.

The Pattern Generator runs at a maximum clock frequency of 100MHz, resulting in a 10ns timing resolution.

The generator has 16 user programmable channels. Eight of those pattern channels are available to the user as so called user Pattern Bits. The remaining bits are dedicated Pattern Bit channels, used for internal synchronisation and IO data control. Two of those dedicated Pattern Bit channels are the stimulus and capture-clock.

**The Capture-clock** is used to sample and store incoming (converted) data for the DIO in capture mode and for all capturing (digitizing) modules in the system.

**The Stimulus-clock** is used to sample the outgoing DIO data, as well as being the sample clock for all generator modules in the system. The capture-clock and stimulus-clock are provided through the backplane to all module slots. The stimulus-clock is also available on the SCSI connector HSO pin.

For fine-tuning of the timing, additional programmable delay lines are put in the capture-clock and stimulus-clock lines.

#### **Clock sources**

The Pattern Generator input clock is selected from a range of clock sources.

- The PLL clock source board

- Backplane Clock, Optionally sourced by one of the installed modules

- An external clock source, connected to the front panel. The front clock input impedance is 50ohms, AC coupled and has a minimum input frequency of 1 MHz. The maximum input clock frequency is 400MHz. The applied clock level may range from 500mVpp to 3.3Vpp. For optimal performance, low clock input levels should be avoided, especially for sinusoid signals.

The Pattern Generator maximum input clock frequency of 100MHz. The mentioned clock sources can therefore be divided by a factor 1, 2, 4, 8 or 16 (for modules with clock source board), or 1..32 (for modules with the PLL clock board).

In addition, HSI or a backplane clock can be chosen as clock source for the Pattern Generator. HSI is an input line coming from the SCSI connector. The backplane clock can be driven by one of the installed modules for synchronized timing with a distinct module clock frequency.

The PLL clock in its turn has a on board 10MHz oscillator reference. The 10MHz PLL clock reference may also be applied externally, on the frontpanel. When an external clock is used as PLL reference, the clock frequency should be 10Mhz.

Clock source selection is managed by the CCS command.

Note: DIO modules with FPGA revision lower than 5 are not equipped with a PLL board. A revision check can be done using the CID command.

#### **Trigger**

Once the module is set in measurement mode, it waits for the trigger to be activated. By default, the trigger is a software trigger, a bit set on receipt of the trigger command **CTRIG\_STATUS**.

Alternatively, a trigger can be supplied from the front-panel and used to synchronize the start of the pattern generation from an external source.

The level sensitivity is depending on the hardware- and FPGA revision.

For new FPGA revisions (5 or above for lowspeed mode, or 4 and above for highspeed mode), the trigger input for the DIO is *high sensitive*.

For older FPGA revisions (below 5 for lowspeed mode, and belof 4 for highspeed mode), the trigger input for the DIO is *low sensitive*.

The trigger input pin has an internal pulldown resistor, so leaving the input open sets the trigger input low.

#### Pattern generator loop trigger

Optionally, the start of each pattern loop of the pattern generator can be controlled by a dedicated pattern loop trigger pin, situated on the SCSI DIO connector pin 32. This is implemented to synchronize the pattern generator loop with external signals, for example a "Conversion ready" signal from a DUT. For more information, refer to the command PB\_MODE.

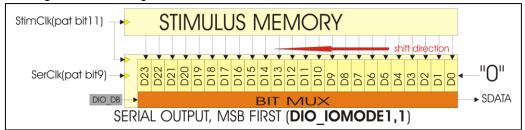

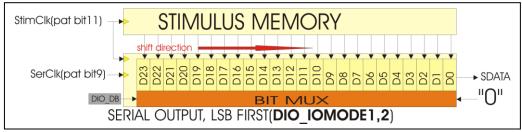

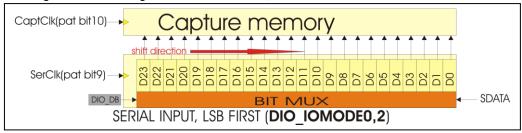

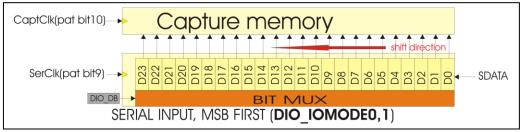

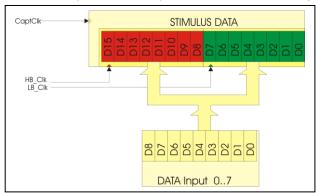

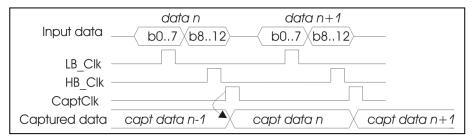

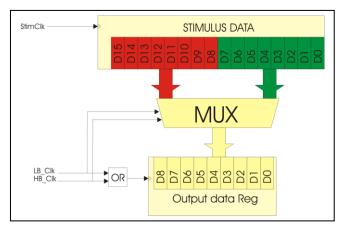

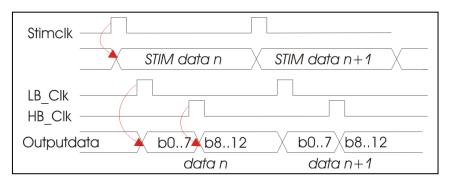

### Stimulus data generation and data capture

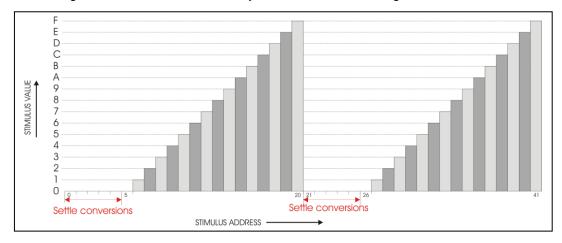

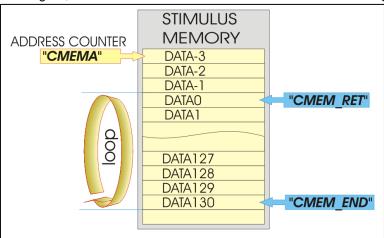

The capture/stimuli memory is 4 Mwordx24 bits. The maximum data rate is 50Mhz. In **stimulus mode**, the StimClk from the Pattern Generator clocks the address counter. For data generation, a user defined part of the memory is used. This way it is possible to store different stimulus signals into different segments of the memory. The segment containing the stimulus data can be repeated (looped) for settling purposes (Settle loops) or averaging purposes (Measurement loops).

In **capture mode**, the CaptureClk increments the address counter. The captured data is stored in the capture memory once the settle loops are finished (the settle loop counter has counted down to zero) Generally, the number of measurement loops is one. Otherwise data of a preceding measurement loop is overwritten.

#### **Data control**

The DIO supports the following IO modes for capturing or generation:

- Parallel The maximum data width is 20 bit, limited by the number of available data IO pins

- Byte by byte The maximum data width 2x 8bits

- Serial data mode The maximum data width is 24 bits, limited by the memory word length.

The timing of the data IO is controlled with dedicated Pattern Bit channels.

# IO levels

The IO levels are adjustable, using the DIO\_IOV command. They can be set to a voltage of 1.2 Volts or to an adjustable voltage between 1.8 and 3.3 Volts (in ca. 256 steps). When the DIO operates in capture mode, it is recommended to adjust the DIO IO level to the IO level applied.

Note: The level of the Pattern Bit channels goes along with the programmed IO level.

# 4.1.3 Digital I/O module in High speed capture mode

This high speed operation mode is set with **DIO\_OPMODE1**. The functional block diagram of the High speed DIO has much in common with the low speed DIO diagram.

The data direction is now set to parallel input and all IO levels are differential LVDS.

The measurement timing is now derived from the clock source selection.

An on board PLL clock source with 10MHz PLL reference is available. Alternatively, the backplane clock or an external clock source, connected to the front panel, can be used. The front clock input impedance is 50 ohms, AC coupled and has a minimum input frequency of 1 MHz and a maximum input clock frequency of 400MHz. The front clock may also be used as 10MHz reference clock source for the PLL clock circuit.

Clock source selection is managed by the CCS command.

The mentioned clock sources can be divided with the Card Clock Divider (see **CCLKDIV** command) by a factor 1, 2, 4, 8 or 16 (for modules with clock source board), or 1..32 (for modules with the PLL clock board).

Note: DIO modules with FPGA revision lower than 5 are not equipped with a PLL board. A revision check can be done using the CID command.

The Trigger signal, either being an external or a software trigger, enables the clock source synchronously. The clock is split into three clocks, each timed with a delay line:

- DUT Clock which is lead directly to the SCSI connector .

- CaptureClk which clocks the capturing module, in this case the DIO capture memory.

- StimClk which clocks the stimulus module, for example the AWG16 module.

The clock that leads to the DIO capture memory is also available on the SCSI connector as DCLK.

The timing relation between stimulus, capture and DUT clock can be adjusted by programming the delay lines with DIO\_CLKDELAY

# 4.1.4 Digital I/O module in High speed stimulus mode

This high speed operation mode is set with **DIO\_OPMODE2**. The functional block diagram of the High speed stimulus mode has much in common with the previously described DIOHS capture mode.

The data direction is now set to parallel output and, again, all IO levels are differential LVDS. The measurement timing is also derived from the selected card clock source, selected with CCS. The same clock sources as described in the HSDIO capture mode are available. The Trigger signal, either being an external or a software trigger, enables the clock source synchronously. The clock is split into three clocks, each timed with a delay line:

- The **DUT clock** and is lead directly to the SCSI connector.

- CaptureClk which clocks the capturing module, for example the WFD16 module.

- StimClk now clocks the DIO stimulus memory.

The stimulus clock that leads to the DIO memory is also available on the SCSI connector as DCLK.

The timing relation between stimulus, capture and DUT clock can be adjusted by programming the delay lines with DIO\_CLKDELAY

# 4.2 DIO II module

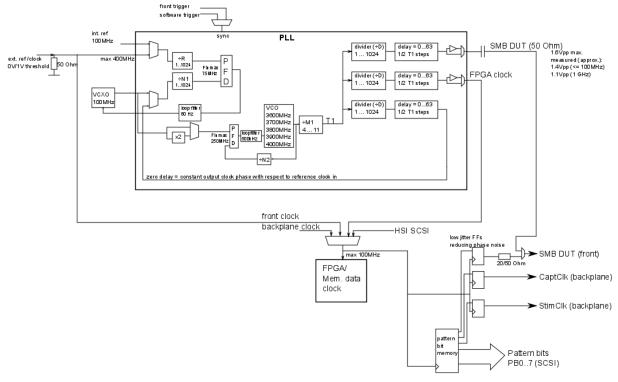

The DIO II module is similar to the DIO module. The main difference is a low jitter clock source.

This module will be identified with PCB revision 5 or higher and driver revision 3.0 or higher. The commands **CINFO?** or **CID** may be used to identify a module.

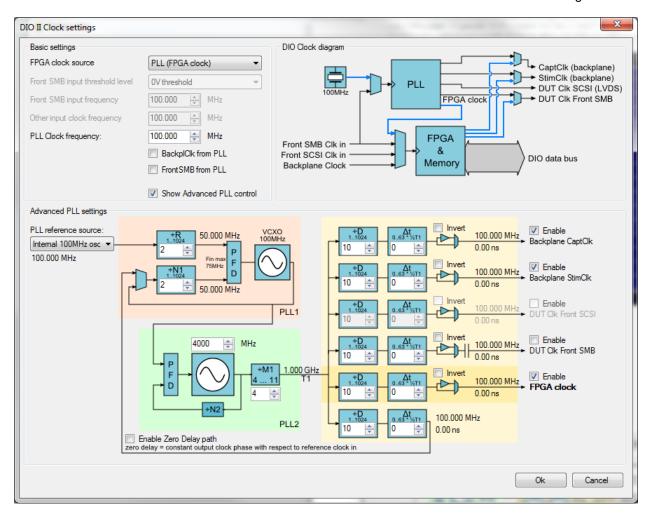

The clock configuration when the DIO module is in low speed mode does have the following layout:

Main differences with respect to the other DIO module in low speed mode are:

- Availability of an SMB DUT clock at the front of the DIO module. This clock source can be an

output of the pattern bit generator (bit 8) or directly from the low jitter PLL output.

- The Stimuli and Capture clock sources can be sourced by the patter bits (default) or by the low jitter PLL (command **DIO\_STIMCAPT\_CLKSEL**).

- The reference input clock may have a frequency up to 400MHz. This value should be filled in at the 3<sup>rd</sup> parameter of CCS

- The Capture and Stimuli clock are synchronized with the PLL FPGA output clock for the best jitter performance.

- PLL output clocks can be individual shifted in phase in 64 steps and divided up to 1024.

The software ATView7006 v1.42 and later includes a window for the new advanced clock settings:

PLL delay = 0...63 1/2 T1 steps CaptClk (backplane) ext. ref/clock 0V/1V threshold 50 Of max 800MHz StimClk (backplane) VCXO 100 MHz delay = 0...63 1/2 T1 steps SCSI DUT (LVDS) delay = 0...63 1/2 T1 steps SMB DUT (50 Ohm) 1.8Vpp max. measured (approx.): 1.4Vpp (<= 100MHz) 1.1Vpp (1 GHz) 1 ... 1024 4000MHz ÷N2 divider (÷D) delay = 0...63 1/2 T1 steps delay = 0...63 1/2 T1 steps divider (÷D) 1 ... 1024 zero delay = constant output clock phase with respect to reference clock i front clock backplane clock max 200MHz FPGA & SCSI DUT (ADC) data clock (Capture mode) memory

sample clock

The clock configuration when the DIO module is in high speed mode does have the following layout:

Main differences with respect to the other DIO module in high speed mode are:

- Availability of an SMB DUT clock at the front of the DIO module. This clock source is directly connected to the low jitter PLL output. Output level can be influenced using the command DIO\_PLL\_CLKOUTLEVEL

- The Stimuli and Capture clock do have a separate PLL clock output and can be programmed at different frequencies using the PLL output divider (commands DIO\_PLL\_ODIV and DIO\_PLL\_CLKCONFIG)

- The reference input clock may have a frequency up to 400MHz. This value should be filled in at the 3<sup>rd</sup> parameter of **CCS**

- PLL output clocks can be individual shifted in phase in 64 steps(command **DIO\_PLL\_PH**) and divided up to 1024 (command **DIO\_PLL\_ODIV**).

- Availability of a DUT data capture clock at the SCSI connector. This clock may be used to capture digital data from and ADC with a data output clock.

- An option to have a constant phase shift between the reference clock input and clock output using the zero delay mode, command **DIO\_PLL\_ZDM**.

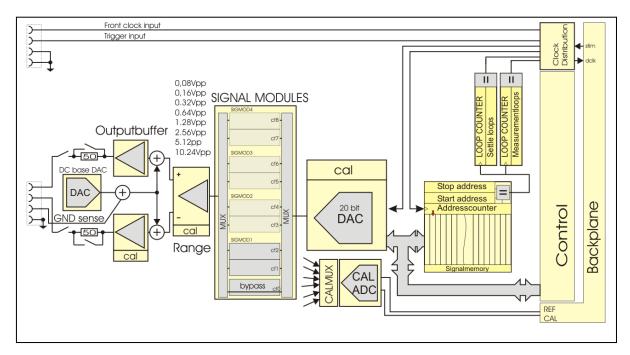

# 4.3 AWG20 20-bit/2Msps Arbitrary Waveform Generator

The AWG20 module is a 20-bit, 2Msps Arbitrary Waveform Generator for medium speed / high resolution waveform generation. The module has 8 output ranges to accommodate different DUT input ranges.

### Output voltage and available signal ranges

The output voltage swing is -10.24V to +10.24V for each output.

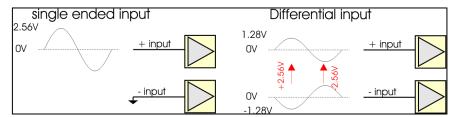

The output range (Signal voltage difference output relative to ground) can be set to: 0.08V, 0.16V, 0.32V, 0.64V, 1.28V, 2.56V, 5.12V, 10.24V (Vpp, single ended). The *differential* output voltage (between both outputs) is twice the programmed output voltage.

# DC offset

The DC offset is added to the signal voltage by the DC offset DAC. The offset voltage range is from -5.12V to 5.12V, programmable in a 9,76uV resolution. The DC offset DAC is always connected to the signal path. The voltage sensed on the ground sense input is added to the programmed offset voltage to compensate for DC voltage loss over the ground connection.

The output voltage is composed as follows:

$$\begin{split} V_{outpos} &= V_{signal} + (V_{dcbase} + V_{gndsense}) \\ V_{outneg} &= -V_{signal} + (V_{dcbase} + V_{gndsense}) \end{split}$$

$V_{outpos}$  is the output voltage relative to ground on the positive force output.  $V_{outneg}$  is the output voltage relative to ground on the negative force output.

V<sub>signal</sub> is the voltage programmed to the signal DAC, either by the CV command or the

stimulus.

V<sub>dcbase</sub> is the voltage programmed to the dc offset DAC, either by the **COV** command.

V<sub>andsense</sub> is the voltage sensed on the GND sense input.

#### Signal module selection

On board there are 4 signal module sockets. Each signal module can be equipped with 2 signal conditioning functions.

By default, there is one signal module installed, containing two low pass filters to remove quantization noise and improve THD at higher frequencies. This signal module carries the following filters:

- 1.2kHz Active 4-pole Butterworth low pass filter selected with command CPATH1

- 12kHz Active 4-pole Butterworth low pass filter selected with command CPATH2

- 40kHz Active 4-pole Butterworth low pass filter selected with command CPATH3

- 200kHz Active 4-pole Butterworth low pass filter selected with command CPATH4

The signal conditioning function of each signal path can be read and is set with **CPATH\_INFO** Placement of extra signal modules, up to a total of 4, is optional. Customized signal modules can be designed for application specific purposes, to add extra ranges or specific filter types.

Alternatively, with command CPATHO, the signal can bypass the signal modules.

### **Connection options:**

The switching of the gate relays can be configured with the CC command in the following ways:

- 1. Both outputs disconnected (CC0)

- 2. Differential, low impedance output with GND sense active (CC1)

- 3. Differential, 50 ohms output with GND sense active ((CC2)

- 4. Differential, low impedance output with GND sense internally connected to AGND (CC3)

- 5. Differential, 50 ohms output with GND sense internally connected to AGND (CC4)

#### Clocks and trigger

The stimulus address counter is clocked either by the stimulus-clock coming from the backplane or by an external clock. The backplane stimulus-clock is generated by the DIO module.

The clock applied will be used as sample clock and stimulus address counter clock and will not be divided on this module. The applied clock frequency is equal to the sample frequency. **The minimum high time of the sample clock is 200ns**.

The external clock can be connected to the backplane DIO clock line and can then be used as clock source for the Pattern Generator. The clock can be switched to the backplane with parameter **o** of the **CCS** command.

In most applications, a software trigger is used to start generation of the signal. Optionally, an external trigger can be applied. An external trigger logic 3.3V TTL level sensitive. Trigger polarity (active low or high) is for the external trigger programmable. Trigger source and polarity are defined with the **CTRIG** command.

### Latency counter

The clock to the signal memory counter can be delayed by a Latency Counter. Optionally, this counter can be programed to create an additional clock latency, which can be seen as a user configurable hold off counter. In normal AD converter measurements, it is not likely to use this function; the Latency counter value should then kept to value 0. For other measurement setups, the hold off feature may be useful.

#### Module auto calibration

For optimum accuracy performance, it is recommended to observe a warming-up period of at least one hour after power up. The module auto calibration should be run at least every three months. An auto calibration can be started with the command "CCAL\_START". The calibration time is dependent of the number of available signal paths, and takes about 10 minutes plus 10 minutes for each signal path. The auto-cal of an AWG module with 2 signal paths takes approximately 30 minutes. Refer to Appendix B: Calibration procedure for details on the auto calibration sequence.

## Front panel LEDs:

The front panel LEDs reflect the status of the module and the channel connection:

# The main module led:

off Module is in configuration mode. green Module is in measurement mode.

red During initialization, self-test, auto-cal. Remains red after self-test error or

initialization error.

# The Channel gate led (small led near the connector):

off Gate relays are open green Gate relays are closed red Channel auto-cal active

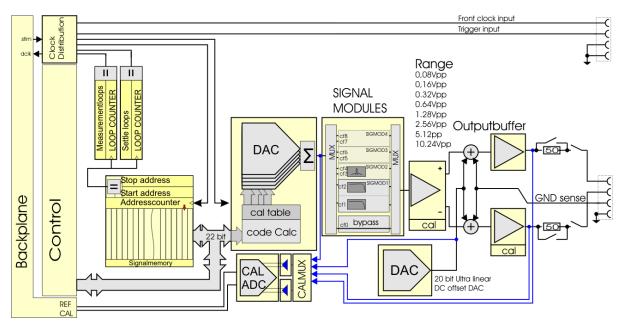

# 4.4 AWG22 22-bit/2Msps Arbitrary Waveform Generator

The AWG22 module is a 22-bit, 2Msps Arbitrary Waveform Generator for medium speed / high resolution waveform generation. The module has 8 output ranges to accommodate different DUT input ranges, and 4 standard filters to further reduce noise and glitch energy.

The AWG22 module is very similar to the AWG20 module, so for most information it's best to refer to the AWG20 information. Differences are described below:

### Output voltage and available signal ranges

The output voltage swing is -10.20V to +10.20V for each output.

The table below shows the available output ranges:

| Range | Single-ended output range (V <sub>PP</sub> , low impedance out) | Differential output swing (V <sub>PP</sub> , low impedance out) |

|-------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| 1     | 10.2                                                            | 20.4                                                            |

| 2     | 5.1                                                             | 10.2                                                            |

| 3     | 2.55                                                            | 5.1                                                             |

| 4     | 1.275                                                           | 2.55                                                            |

| 5     | 0.6375                                                          | 1.275                                                           |

| 6     | 0.31875                                                         | 0.6375                                                          |

| 7     | 0.159375                                                        | 0.31875                                                         |

| 8     | 0.0796875                                                       | 0.159375                                                        |

The DC-offset range is -5.10V to + 5.10V

The module does have a pipe line of 2 clock cyles. So the first output voltage is available at the 3<sup>rd</sup> clock cycle. The initial voltage is determinded by the commands CV and COV.

### Calibration

For optimum accuracy performance, it is recommended to observe a warming-up period of at least one hour after power up. The module auto calibration should be run at least every three months. An auto calibration can be started with the command "CCAL\_START". The calibration time is dependent of the number of available signal paths, and takes about 10 minutes plus 10 minutes for each signal path. The auto-cal of an AWG module with 2 signal paths takes approximately 30 minutes. Refer to Appendix B: Calibration procedure for details on the auto calibration sequence.

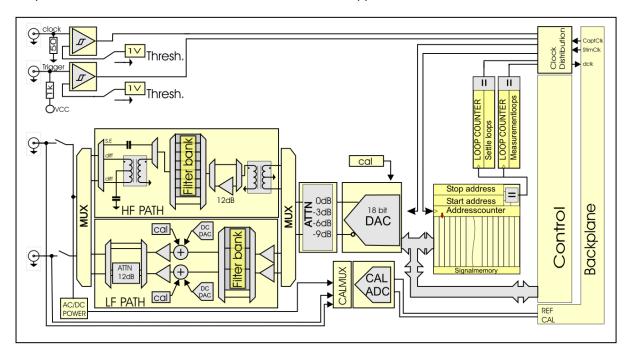

# 4.5 AWG18 18 bit / 300Msps Arbitrary Waveform Generator

The AWG-18 module is a 18-bit, 300Msps Data update rate waveform generator, for high frequency signal generation. In combination with a user selectable 2x or 4x or interpolation filter, the DAC is capable of sampling at a frequency up to 1.2GHz. The maximum generated signal frequency is 150MHz, limited by the maximum 300Msps data rate. Interpolation reduces the influence of sin(x)/x at high signal frequencies. The maximum DIO-generated clock frequency is 200MHZ. For Sample frequencies above 200MHz, an external clock should be applied.

### Ranges

The following ranges can be set:

| ne rollowing ranges out be set. |                               |                                    |                             |                               |  |

|---------------------------------|-------------------------------|------------------------------------|-----------------------------|-------------------------------|--|

| Range                           | HF Path, Single-Ended         | HF Path, Differential              | LF path (per output)        | LF path (per output)          |  |

|                                 | (V <sub>PP</sub> in 50Ω load) | $(V_{PP} in 100\Omega diff. load)$ | (V <sub>PP</sub> , no load) | (V <sub>PP</sub> in 50Ω load) |  |

| 0                               | 4.6286                        | 6.5536                             | 6.5536                      | 3.2768                        |  |

| 1                               | 3.2768                        | 4.6396                             | 4.6396                      | 2.3198                        |  |

| 2                               | 2.3198                        | 3.2846                             | 3.2846                      | 1.6423                        |  |